嵌入式裸机程序之系统时钟

1.系统时钟

S3C2440有三种时钟:FCLK(用于CPU核),HCLK(用于主机模块),PCLK(用于外设).两种PLL(锁相环):MPLL(用于设置FCLK,HCLK,PCLK),UPLL(用于设置USB设备)。如图所示:

2.系统时钟初始化

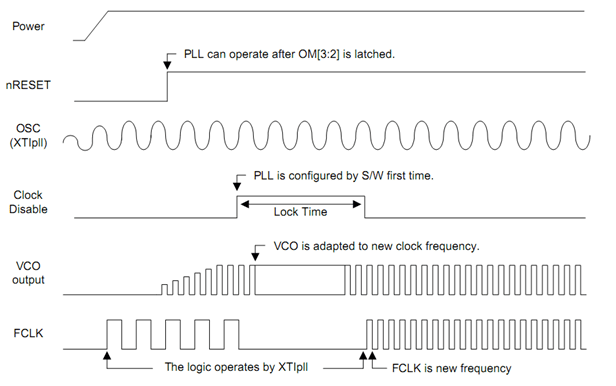

S3c2440系统时钟初始化流程如下:(1) 系统刚上电几毫秒后,FCLK等于外部晶振的振荡频率,即FCLK=Fin(2) 当复位信号nReset恢复高电平后,锁相环按照寄存器MPLLCON和CLKDIVN设定的倍频比例开始生成所需要的时钟频率。从锁相环开始工作到输出新的稳定的频率值需要一定的时间(lock time 即锁相环的捕获时间),经过这段时间后,锁相环输出新的频率值,这是FCLK等于锁相环的输出。

如图所示:

3.代码解析

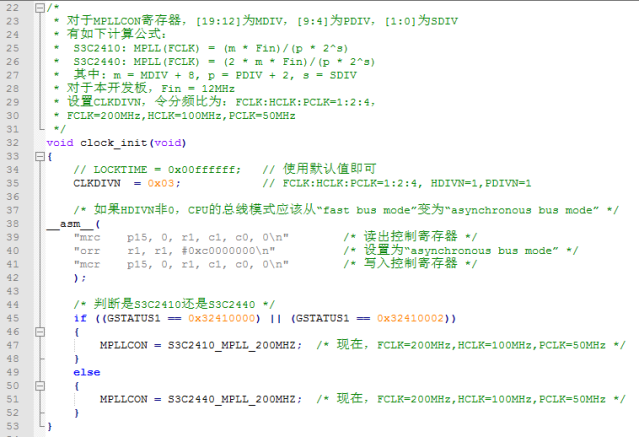

代码如下所示,首先设置FCLK、MCLK、PCLK的分频比例,随后根据S3C2440的芯片手册说明,当HDIV非1时需要执行一段代码。然后就可以设置MPLLCOM寄存器,设定锁相环输出频率了。

嵌入式裸机程序之系统时钟

http://atime.cc/2017/02/10/嵌入式裸机程序之系统时钟/